# The MOS Silicon Gate Technology and the First Microprocessors

### **Federico Faggin**

This is a preprint of the article published in La Rivista del Nuovo Cimento, Società Italiana di Fisica, Vol. 38, No. 12, 2015

# 1. – Introduction

There are a few key technological inventions in human history that have come to characterize an era. For example, the *animal-pulled plow* was the invention that enabled efficient agriculture, thus gradually ending nomadic culture and creating a new social order that in time produced another seminal invention. This was the *steam engine* which gave rise to the industrial revolution and created the environment out of which the *electronic computer* emerged – the third seminal invention that started the information revolution that is now defining our time.

All such inventions have deep roots and a long evolution. Engines powered by water or wind were used for many centuries before being replaced by steam engines. Steam engines were then replaced by internal combustion engines, and finally electric motors became prevalent; each generation of engines being more powerful, more efficient, more versatile, and more convenient than the preceding one. Similarly, the origin of our present computers dates back to the abacus, a computational tool that was used for several millennia before being replaced by mechanical calculators in the 19<sup>th</sup> century, by electronic computers in the 1950's, and by microchips toward the end of the 20<sup>th</sup> century.

The invention of the electronic computer was originally motivated by the need for a much faster computational tool than was possible with electromechanical calculators operated by human beings. This improvement was accomplished not only by performing the four elementary operations considerably faster than previously possible with calculators, but even more importantly, by adding the ability to program a long sequence of arithmetic operations that could be executed *automatically*, without human intervention. The addition of *programmability*, proved to be an immensely fruitful and versatile capability, allowing computers to soon become *universal symbol manipulators*, with countless new applications, far exceeding what even programmable calculators were originally intended to do.

Toward the end of the 20<sup>th</sup> century, the relentless progress in microelectronics combined with the digitization of all types of information, made computers so powerful, small, low-cost, and pervasive that many functions that previously required separate, single-function devices were subsumed by a single programmable mobile computer capable of handling the individual's needs for communication, computation, control, and storage of all kinds of information, be it numbers, text, images, sound, or video.

This paper will describe the history of two key inventions: the MOS silicon gate technology, and the microprocessor. These were the two developments that made it possible to replace huge and costly machines with pocket-size devices many thousands of times less expensive, and thousands of times more powerful than the early computers. This remarkable progress was due to the power and flexibility of microelectronics, the technology that provided the early transistors used in the second-generation computers.

What's remarkable is that while in the late 1950's transistors were just one of the *many* key components necessary to build a computer, less than 20 years later an entire monolithic computer could be built in a single chip of silicon, in the same physical volume that previously housed a single transistor!

This progress is unprecedented because in less than 30 years, a single chip weighting less than one gram, occupying a volume smaller than a cubic centimeter, dissipating less than one Watt, and selling for less than ten dollars could do more information processing than the UNIVAC I, the first commercial computer, which used 5200 vacuum tubes, dissipated 125 kW, weighted 13 metric tons, occupied more than 35 m<sup>2</sup> of space, and sold for more than one million dollars per unit.

Viewed from today's perspective, the early giant computers of the 1950's and '60's provided precisely the architectural blueprints of the type of symbol manipulator that the world needed. The microelectronics industry then did the rest, bringing the cost, size, and energy requirement down to the point where a computer could fit inside an electric toothbrush, a hearing aid, or an inexpensive toy – applications that were not only unimaginable, but even *incongruous* when computers were room-sized and cost millions of dollars.

After a brief history of microelectronics and computers, this paper will describe, from a first-person basis, the development of the silicon gate technology (SGT) at Fairchild Semiconductor, and the development of the early microprocessors (MP) at Intel, the two inventions that gave new life and impetus to the information revolution that began in the mid 1940's with the development of the first mainframe electronic computers using vacuum tubes.

## **2.** – A brief history of microelectronics

Microelectronics officially started with the invention of the first transistor at Bell Laboratories in 1947 by John Bardeen, Walter Brattain and William Shockley, just one year after the first electronic computer, the ENIAC, was realized at the University of Pennsylvania. No one ever imagined at that time that these two inventions would merge, less than 30 years later, into a microchip, changing society in a fundamental way.

By replacing the electro-mechanical relays used in previous generations of calculating machines with vacuum tubes, the operating speed of ENIAC was increased by more than a factor of 1,000. This increase in speed came at a cost — vacuum tubes were bulky, power-hungry, and most of all, *unreliable*. The short meantime between failures in a single vacuum tube was a crippling problem for a computer needing thousands of them. Considering the reliability issues that then plagued electronic equipment, vacuum tube computers were over 10 times more likely to malfunction when compared to the most complex electronic equipment of that time. The search for a viable vacuum tube replacement with a more reliable, smaller, power-efficient, and lower cost solid state device had been ongoing since the 1920's. The first patent for a semiconductor "triode" was filed in 1925 by Julius Edgar Lilienfeld, and a more advanced device was patented by Oskar Heil in 1934. Both devices were *field-effect devices*, similar in principle to the current MOS transistors, but no commercial devices were ever produced.

The first Bell Labs transistor was a point-contact device, commercialized in 1948 by Raytheon with model CK703. However, point-contact transistors were too difficult to

build and too fragile to be useful, since even a modest mechanical shock could put an end to their operation. A new operating principle was needed. It was the breakthrough work of W. Shockley on diffusion transistors that introduced the new operating principles used in all modern bipolar transistors. This original work led to the first commercial *alloyjunction* transistors introduced by GE and RCA in 1951. From that point on, new applications for bipolar transistors started to grow rapidly – among them, the first hearing aids and portable radios – and in 1953, one million transistors were produced in the US alone.

All early transistors used a tiny single-crystal of germanium as their starting semiconductor material, and were built *one at a time*, just like the vacuum tubes. It was soon realized, however, that a better semiconductor material was necessary, since the temperature effects on germanium transistors could cause a thermal runaway with the self-destruction of the transistor. This unwanted effect was due to the rather narrow bandgap (.66 eV at 300K) between the conduction band and the valence band of germanium crystals. Furthermore, the operating frequency of germanium transistors was rather limited. A better material, silicon, with a bandgap of 1.11 eV at 300K, was soon identified, and silicon junction transistors were introduced commercially for the first time by Texas Instruments (TI) in 1954.

In 1957, a new company, Fairchild Semiconductor, was started in the San Francisco Bay Area by eight key engineers abruptly leaving Shockley Semiconductor. Among them were Robert Noyce, Gordon Moore, Jean Hoerni, and Jay Last. Fairchild's mission was to develop advanced bipolar junction transistors made with silicon to serve the needs of the emergent aerospace industry. Just for size, in 1957 the total production of transistors in the US was 29 million units. Today, a single chip costing less than \$1 may easily contain more than 30 million transistors, including all their interconnections.

Before long, Fairchild Semiconductor became the leading company in the nascent microelectronics industry due to the seminal invention of the *planar process* by Jean Hoerni, a Swiss engineer. Up until that time, transistors had been fabricated one at a time. With the planar process, *many* transistors could be simultaneously fabricated, one next to the other, on the surface of a thin slice (called wafer) of a single-crystal silicon ingot. The planar process truly revolutionized the industry because it not only dramatically reduced the size and cost of transistors, but far more importantly, it made possible the monolithic integrated circuit (IC).

Hoerni's process consisted in fabricating an array of identical transistors on the surface of a silicon wafer with the diameter of less than one inch. This was done by recognizing that silicon dioxide could mask the diffusion of dopants in silicon. Therefore, the silicon doping necessary to create semiconductor junctions in specific places, could be achieved by first thermally growing a layer of silicon dioxide on the surface of a silicon wafer, and then opening windows in the oxide where the junctions were needed. The windows were defined by using photolithography followed by etching, a technique already in use to make printed circuit boards.

After the removal of the oxide by chemical etching in the areas not protected by the developed photoresist, the junctions could then be created by thermal diffusion of the appropriate dopants into the silicon. By using a sequence of thermal, chemical, and masking steps simultaneously affecting all transistors, it was possible to produce a batch of many identical transistors on the surface of a wafer. After the wafer was completed, it

was then cut into the individual transistors that were packaged into discrete components in the final step of the process.

With the invention of the planar process, it was straightforward to recognize that the transistors sitting next to each other could also be directly interconnected on the wafer itself, rather than being separated and individually packaged, only to be re-assembled and interconnected in a printed circuit board. What was missing was a process to directly *insulate* each transistor in the wafer so that the transistors would not interfere with each other – a process that was not needed when the transistors were physically cut and individually packaged. Bob Noyce, the head of Fairchild Semiconductor, invented a process to do so, making it possible for the first time to fabricate a truly *monolithic* integrated circuit (IC). It was 1961, and the first commercial IC, a simple resistor-transistor logic gate (RTL), was designed by Fairchild's Jay Last, and was first sold in 1962. A short ten years later, the microprocessor was born.

The history of the integrated circuit is another example clearly showing how most seminal ideas have roots that go back in time much beyond what is normally acknowledged when the history of the invention is written by the victors. The *idea* or conception of the integrated circuit was first presented at the US Electronic Components Symposium on May 7, 1952 by Geoffrey Dummer, who then asserted: "it now seems possible to envisage electronic equipment in a solid block with no connecting wires." This occurred at the same time when the industry had just managed to successfully fabricate the first diffused-junction bipolar transistors. But Dummer was never able to bring his idea into a working device, despite trying for many years.

TI's Jack Kilby, who won the 2000 Nobel Prize in Physics for his contributions to the invention of the IC, is credited with making the first commercial integrated circuit in 1959. This circuit, however, was *not a monolithic* IC, because it required the individual positioning of *separate* solid-state components inside a small package followed by manually wiring them in situ. The interconnection of the separate components was supposed to eventually be performed in a single operation. However, that idea was never commercially realized. It was Hoerni's planar process combined with Noyce's transistor insulation process that provided the first *practical* method to fabricate monolithic ICs; a method that was soon universally adopted by the world's microelectronics industry.

Planar transistors and ICs were initially very expensive, limiting their early applicability primarily to the US missile and space program where size, power dissipation, and reliability were of paramount importance. However, the inherent potential of the planar process was huge because over time, the cost of a single transistor within an integrated circuit could be dramatically reduced by increasing the wafer size and reducing the physical dimensions of the transistor. Thus more ICs, each integrating more and more transistors, could be simultaneously batch-fabricated in a single silicon wafer.

The advantages of using ICs over discrete transistors were many and compelling, as long as it was possible to *standardize* the functions being performed by the ICs (the cost of an IC depends dramatically on the unit volume produced). However, the circuit designers that previously used discrete components to create a large variety of different circuits, resisted the idea of standardization, slowing down the early adoption of ICs. As the cost of ICs diminished and more standard building blocks became available, rationality prevailed and these early difficulties were gradually overcome. With the development of the microprocessor, the boundary of standardization was pushed beyond the individual circuits to an entire system.

By the mid-sixties the cost of ICs had become low enough to enable many new industrial and commercial applications, leading to a market expansion and thus to lower cost-per-function. This in turn led to the emergence of new *consumer* applications, fueling the virtuous cycle responsible for the establishment of a vigorous and rapidly-growing semiconductor industry.

In 1965, Gordon Moore noticed that the number of transistors in an IC for which the cost per transistor was nearly minimized, had been doubling every year since 1962. He boldly predicted that this trend would continue for the following 10 years. This observation became known as Moore's law, forecasting an exponential growth of the number of transistors in an IC. Of course Moore's law is not a physical law, and therefore the doubling-time must increase over time, as more and more physical limitations are progressively reached. And eventually the process must halt when the transistor size approaches the atomic size. In fact, the doubling time has gradually gone from one year in 1963 to three years in 2013, averaging two years for the period 1970-2014. But since the doubling-time increases slowly with time, Moore's Law has been a good predictor of the number of transistors that can fit in future generations of ICs, and thus it has served very well as a valuable planning and forecasting tool.

All early ICs used *bipolar* transistors whose principle of operation is essentially identical to the early discrete diffusion transistors made with germanium or silicon. In 1959, the same year the planar process was invented at Fairchild Semiconductor, the MOSFET (Metal Oxide Semiconductor Field Effect Transistor) was invented by Dawon Kahng and John Atalla at Bell Labs. This was another seminal invention. The MOSFET, or simply MOS transistor, works by using a different operating principle than bipolar transistors. In the MOS transistor, the signal amplification is achieved by controlling the conduction of charge carriers at the *interface* between silicon and silicon-dioxide. This is accomplished by changing the voltage applied to a *gate* electrode sitting atop a thin insulating layer of silicon dioxide that bridges two back-to-back junctions (called *source* and *drain*). In a bipolar transistor instead, the conduction depends on the *bulk diffusion* of carriers within the *volume* of silicon (the base) in common with two back-to-back junctions. The three terminals connecting the back-to-back junctions are called emitter, base, and collector; with the emitter-base junction forward biased and the base-collector junction backward biased.

MOS transistors have the important feature of being self-isolating. Therefore, they are simpler to manufacture and quite smaller than bipolar transistors. Even more importantly, they are *surface-effect* devices, therefore their physical size can be proportionally scaled down much more easily than bipolar transistors, a capability that was not recognized at the time of their invention, but later became the basis for the dimensional scaling of transistors that fueled Moore's law for the last 50 years.

In the early 1960's, however, MOS transistors had speed and reliability characteristics that were much worse than bipolar, and were generally considered a second-best alternative to make ICs, except for a class of less-demanding applications where cost more than performance or reliability were of paramount importance. It took many years for the industry to learn how to fabricate reliable MOS devices. The key development to bring MOS technology to maturity was the silicon gate technology (SGT) invented at Fairchild Semiconductor in 1968 by Federico Faggin and Tom Klein.

With SGT, it became possible to make <u>reliable</u> MOS ICs that were 5 times faster and had twice the number of transistors per unit area than MOS ICs made with aluminum gate (for random logic circuits). With SGT new categories of devices could also be produced, such as dynamic random access memories (RAMs) (difficult to fabricate with metal gate due to the high junction leakage of metal-gate transistors), image sensors using charged coupled devices (CCD), non-volatile memories, sophisticated analog ICs, and microprocessors.

For the first time in the history of computers, all the key components necessary to implement a general-purpose computer could be made with the same technology, leading naturally to a *monolithic computer*. SGT was also the core technology that allowed the scaling of MOS transistors for the following 40 years, eventually replacing bipolar technology in nearly all applications.

# 3. – A brief history of computers

As mentioned in the introduction, the roots of modern computers go back to the abacus. Therefore, they are far deeper than the roots of microelectronics which are based on electromagnetism and quantum physics: unknown physics before the XIX and XX centuries respectively. The abacus dates back at least 4600 years, and is the first known instrument to aid human beings in performing arithmetic calculations. We have to go forward about 4200 years to find the first example of the next milestone: a mechanical calculator invented by Blaise Pascal in 1642, called Pascaline. Since this machine could only perform additions and subtractions, however, its usefulness was quite limited. In fact, a skilled abacus user could compute faster than a skilled Pascaline user.

In 1673, Gottfried Leibnitz devised a conceptual method for mechanically performing multiplications and divisions, but the technology of his day did not support the fabrication of such devices. We have to wait another 178 years before the first four-function mechanical calculator entered production. This mechanical calculator was called Arithmomètre. It was invented by Tomas de Colmar and it was made commercially available for the first time in 1851, exactly 100 years before the first commercial electronic computer was sold. This machine was sturdy and practical enough to be used routinely, launching an industry that lasted until the 1970's when the electromechanical calculator was superseded by electronic calculators based on microchips.

The first *programmable* machine was the Jacquard loom, invented by Joseph Marie Jacquard in 1801 to automatically weave complex patterns in textiles. The loom was controlled by punched cards that stored the "program" directing the step-by-step operation of the loom. The Jacquard loom was a highly successful invention, and is also the first example of an automatic system controlled by a program; a procedure that can be changed without changing the machine itself. It is a forerunner of modern computers, though on the surface, it appears to have little in common with computers.

The idea of using punched cards was later employed by Herman Hollerith to produce an electromechanical tabulator that could rapidly sort data. This device was used to compile the data of the 1890 US census, demonstrating great improvements over manual sorting. Interestingly, Hollerith was the founder of Tabulating Machine Company, which later changed its name into IBM.

Another important area of development was associated with automatic telephone exchanges based on relay commutators (relays were invented in 1835 by J. Henry and improved over the years). This application area formed another major thread that was later woven into the modern computer design. Victor Shestakov in Russia and Claude Shannon at Bell Labs in the US, in the period between 1935 and 1937, independently "discovered" that Boolean logic – a binary logic developed in the 1840's by Charles Boole – was the perfect mathematical formalism to describe switching systems and calculating machines.

In an unrelated development, Alan Turing in England invented the Turing Machine in 1936. It was a mental experiment that he used to falsify Hilbert's Decision Problem, posed by the mathematician David Hilbert in 1928. His Universal Turing Machine provided an abstract model to describe a class of machines capable of executing any general algorithm, thus giving birth to theoretical information science.

All the threads I mentioned earlier came together in 1941 with the realization of the first fully functioning Turing-complete electromechanical computer, the Z3, designed and built by Konrad Zuse in Germany. This machine used a binary floating-point architecture based on 22-bit words and a CPU made with about 2300 relays. The read-write memory (write once) to store programs and data was ingeniously implemented by using 35 mm punched film (the same film used in cameras). The clock frequency was about 5 Hertz, which makes us smile now, considering that microchips today have clock frequencies of several GHz. The Z3 takes us to the threshold of the electronic computer era.

Electronic computers started in 1943 with a secret project financed by the US Army to develop a computer capable of rapidly calculating ballistic trajectories. The major new idea was to replace relays with vacuum tubes to increase the computational speed by at least a factor of 1000. The result was ENIAC, the first fully functional electronic computer designed and built by J. Mauchly and P. Eckert, and completed in 1946. ENIAC had an instruction cycle of 200 microseconds and the program was provided by plugboards and switches, a fairly rudimentary and laborious method. It employed 17,468 vacuum tubes, occupied an area of 167 m<sup>2</sup>, dissipated 150 kW of power, and weighted 30 tons. The meantime between failures was a few hours, due to the poor reliability of the vacuum tubes.

ENIAC however was not yet a complete solution because it lacked the ability to store a program in its electronic memory. Therefore, the first electronic computer to have all the essential features of the modern machines was the EDSAC, the first *stored-program computer* developed at Cambridge University by M. Wilkes, with the collaboration of the famous mathematician John von Neumann, who was the one suggesting to use the same memory that stored data to also store the programs. The EDSAC was completed in 1949 and its program and data memory was realized with a serial memory using a mercury delay line with 1024 17-bit words. The modern random access memory (RAM) had not yet been invented.

All early computers were one-of-a-kind research machines, until the introduction of the first commercial electronic computer in 1951. This machine was the UNIVAC I, which was a stored-program machine with a *serial* main memory of 1024 12-bit words. The UNIVAC I used for the first time a magnetic tape secondary memory to increase the

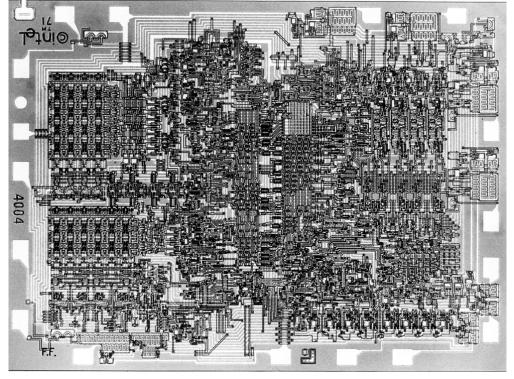

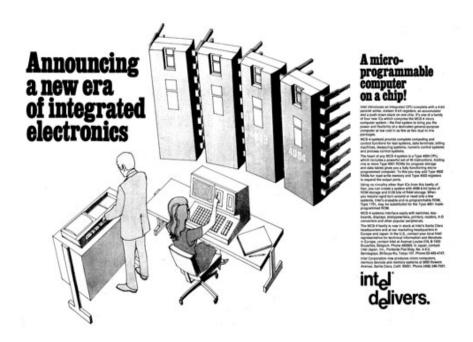

overall memory. Capable of executing 500 multiplications per second, UNIVAC I used 5200 vacuum tubes dissipating 125 kW, and sold a total of 46 units at more than one million dollar per unit, demonstrating for the first time the commercial viability of computers. Twenty years later, the first single-board computer using the Intel 4004 microprocessor had similar performance to the UNIVAC I in a single printed circuit board of 25x25 cm<sup>2</sup> dissipating approximately 10 W and costing a few hundred dollars! Less than ten years later, that single-board computer could be integrated into a single chip – a *monolithic computer*.

All early mainframe computers used vacuum tubes until 1957, the year when the first commercial transistorized computer, the Philco Transac S-2000, was introduced. Two years later, the Olivetti Elea 9003, and the IBM 7090 transistorized computers were also commercialized. From that point on, all new computer models used transistors. With transistors, the size, power dissipation, speed, and especially the reliability of computers were drastically improved. This was the coming of age of computers, and from this point on computers showed their worth and versatility in a rapidly growing variety of applications.

The 1960's marked a period of rapid evolution for computers, from very large to very small, from minicomputers to supercomputers. For example, in 1963 the SAGE system began operation. Designed by IBM in collaboration with the US Air Force to coordinate the operations of 24 radar stations in Northern America, SAGE became the largest computer ever built (area: 2000 m<sup>2</sup>; weight: 275 ton; power consumption: 3MW) and created the world's first real-time computer network. In 1964 IBM introduced the System/360, a large family of compatible and scalable computers capable of covering a wide range of applications. It became a highly successful product line with novel software, like the first sophisticated operating system. That same year, Control Data Corporation introduced the CDC 6600 the world's first supercomputers, a trailblazing supercomputer company for many years. The CDC 6600 cost more than \$8 million and was 10 times faster than the fastest computer of that time.

By 1965, the commercialization of a family of logic ICs allowed the reduction of the size of computers to that of a small cabinet, or a large box, giving birth to the *minicomputer*. The minicomputer was a scaled down version of a mainframe computer, intended for applications where mainframes were too big and too costly to be usable. First introduced by Digital Equipment Corporation (DEC) with the model PDP-8, minicomputers opened up new application areas for computers, particularly for communication and for all types of control systems, further expanding their reach.

The versatility of the computer is obviously due to its programmability. Therefore, the hardware alone is not sufficient to solve any particular problem; one also needs a program that once loaded in the memory of the computer, makes the hardware-software combination perform the desired function. The creation of software necessary to handle specific functions started a parallel development to the computer hardware, marking the beginning of the software industry. Furthermore, since a computer is a *universal* symbol manipulator, as computers became faster and more affordable, more and more applications could be performed with appropriate software. In several cases the applications appeared initially incongruous with the expectation of what a computer should be able to do; for example, speech recognition, playing chess, or processing video.

Over time, the percentage of the total information processing investment dedicated to software grew, while the cost of the hardware decreased. Today the preponderant cost resides in the software.

The art of programming relies on the ability to conceptualize the solution to a problem, or task, into a series of algorithms – procedures that a computer can efficiently execute. The importance of programming has grown dramatically with far reaching consequences.

Although it is beyond the scope of this paper to explore this new field of human endeavor, I wish to at least underscore that the information revolution that is sweeping society has brought to the forefront the deep and unsuspected relationship between the nature of information and the nature of reality. This is a particularly fascinating subject that was completely unknown to physicists and philosophers until the 1960's; a subject that in my opinion will shape a new sense of self and a new sense of reality in human society, with major social consequences.

We have now reached the state of the art at the time when the inventions of the SGT and the microprocessor occurred, as will be described in the rest of the paper.

## 4. – The invention of the MOS silicon gate technology

### 4.1 The state-of-the-art in the mid-Sixties

As mentioned earlier, more than 95% of all commercial integrated circuits manufactured in 1967 used bipolar transistors. Compared to bipolar, MOS transistors were surfaceeffect devices of simpler construction, fabricated using similar processing steps, but in a different sequence. However, that simplicity did hide a major difficulty: MOS devices were very sensitive to the presence of impurities in the manufacturing process. In particular, even an infinitesimal amount of sodium could contaminate the IC causing a substantial threshold voltage drift over time that could render the IC useless in the field.

The MOS technology had two key advantages over bipolar: (1) higher circuit density by a factor of 5 to 10; and (2) lower power dissipation by a factor of 5 to 10. But its speed in the mid 1960's was about 50 times lower than bipolar, limiting its usefulness to a short list of applications. Overall, it was generally believed that MOS circuits were too slow and too unreliable to ever challenge the market dominance of bipolar technology.

The prevalent MOS process technology of that time used enhancement mode, Pchannel MOS transistors with gates made of aluminum, the same metal that was used to interconnect the transistors within an IC. The standard MOS fabrication process started by thermally growing the field oxide in a [111]-orientation silicon wafer, followed by masking and etching the field oxide in the regions where the source and drain of the MOS transistors had to be located. The process continued with the following steps: (1) doping the source and drain regions with boron, (2) growing some additional thermal oxide over the exposed source and drain regions, with the concomitant diffusion of the boron, (3) removing the field oxide in the gate region of the transistor, and growing a thin oxide, the gate oxide. After the gate oxide growth, contact areas to the source and drain junctions were defined and etched, followed by aluminum deposition, masking and etching to create the gate electrodes and the interconnections. The final passivation step consisted in the vapor deposition of a layer of silicon dioxide (called *vapox*) over the entire structure, followed by etching the vapox over the aluminum pads. The pads were large aluminum areas located at the edges of the chip where thin aluminum wires were ultrasonically bonded to the package.

Due to the inevitable misalignment of the gate mask with respect to the source and drain mask, it was necessary to have a fairly large overlap area between the gate region and the source and drain regions of the transistor, to insure that the channel controlled by the gate would positively bridge both source and drain under worst-case misalignment of the gate mask. This requirement resulted in a significant increase in the gate-to-source and gate-to-drain parasitic capacitances, over and above the amount that would be strictly necessary if perfect alignment was possible, causing a major performance degradation.

The threshold voltage of the transistors was in the range of -4 to -9 volt, dictated primarily by the crystal orientation and the resistivity of the silicon wafer, the gate oxide thickness, and the work-function difference between aluminum and silicon. To maintain the isolation of the various transistors within the IC, it was essential that the threshold voltage of the parasitic MOS transistors be higher than the supply voltage<sup>1</sup>. This requirement was accomplished by using a sufficiently thick field-oxide; and the higher the supply voltage, the higher the thickness of the field oxide had to be.

However, increasing the thickness of the field oxide interfered with the integrity of the aluminum interconnections going over the oxide steps, due to the thinning out of the aluminum at those steps. This effect could potentially create severe reliability problems in the field due to electro-migration<sup>2</sup>, and also cause major yield problems if the metal did break. The high threshold voltage MOS technology being used at that time achieved a delicate balance between the various conflicting requirements with only a small safety margin.

The ideal conditions for MOS technology would have been to use wafers with [100] crystal orientation, instead of the [111] orientation used in the high-threshold-voltage process, because that change would have caused the threshold voltage of the MOS transistors to be in the range of -2 to -5 volt, allowing the supply voltage to go from -24 to -15 volt, with the major benefit of halving the power dissipation for the same speed. Unfortunately, with [100] starting material, the field threshold voltage was lower than the supply voltage for the maximum allowed field-oxide thickness. The only solution then was to use N+ "channel-stoppers," which were diffusions underneath the field oxide to raise the field-oxide threshold voltage. However, this solution was undesirable because it required an additional masking step, and even more importantly, it drastically reduced the circuit density, increasing the cost of the IC; a hardly worthwhile tradeoff. In the mid-Sixties, the industry was still trying to find a way to reduce the MOS transistor threshold voltage without sacrificing the circuit density.

<sup>(&</sup>lt;sup>1</sup>) A parasitic MOS transistor is an unintended transistor obtained when a metal line over the field oxide crosses two junctions. In this case the junctions act as the source and the drain of a parasitic MOS device, with the metal line acting as the gate of such device. If the voltage on the metal line is higher than the threshold voltage of the parasitic MOS (called the field-oxide threshold voltage), a stray conduction path between the two junctions is created. Therefore, if there is a voltage difference between the two junctions, a stray current will flow between them, rather than the junctions being isolated. This possibility is particularly damaging in the case of dynamic circuits because electrical charges stored in MOS transistor gates may rapidly leak away through this unwanted stray paths, causing malfunctions.

$<sup>(^{2})</sup>$  Electro-migration causes the aluminum interconnects to open before the expected lifetime of the device if the current density in the aluminum exceeds a certain limit. The thinning of metal lines over the oxide steps caused by self-shadowing during the aluminum vacuum deposition process could lead to such problem in the field, creating a major reliability hazard.

The other major limitation of MOS technology was the very high parasitic gate-tosource and gate-to-drain overlap capacitances – a widely recognized problem with no known solution. The overlap capacitance with the most adverse consequences on circuit performance was the gate-to-drain parasitic capacitance, Cgd. Due to the well-known Miller effect, the effective gate capacitance of any given transistor is increased by its Cgd multiplied by the gain of the circuit of which the transistor is a part. Since the gain is generally much greater than one, the impact of Cgd on the switching speed of the transistor is considerable. Furthermore, since the variability of Cgd due to the unpredictable direction of the misalignment is very high, some wafers would be impacted very little and some other wafers would be impacted very much, producing a large and undesirable spread in the speed of the ICs produced.

By 1967 much of the MOS industry was engaged in developing a low threshold voltage MOS technology to replace the incumbent technology. This objective was eventually achieved with the SGT in 1968, and with aluminum-gate devices through the use of ion implantation, in 1969-1970. Ion implantation was a new technology that allowed doping silicon in highly controllable amounts, far and beyond what was possible with thermal doping, particularly for low doping concentrations, which were nearly impossible to achieve with thermal doping. Ion implantation was the cure to increase the field-oxide threshold voltage with [100] oriented silicon without channel stoppers. With SGT, instead, the MOS threshold voltage was reduced without having to use [100] material or ion implantation. But most importantly, the parasitic overlap capacitance problem and the reliability problems were also permanently solved, as we will see below.

### 4.2 The self-aligned gate

In 1966 Robert Bower realized that if the gate electrode was defined first, the channel boundaries of the source and drain regions would be "*self-aligned*," thus avoiding the overlap between the source-drain mask and the gate mask. This method would not only minimize the parasitic overlap capacitances, but it would also make them insensitive to misalignment. He proposed a method in which the aluminum gate itself was used as a mask to define the source and drain regions of the transistor at the gate-region boundaries. However, since aluminum could not withstand the high temperature required for the conventional thermal doping of the source and drain junctions, Bower proposed to use ion implantation, a new doping technique still in development at Hughes Aircraft, his employer, and not yet available at other labs.

While Bower's idea of using the aluminum gate as a mask to define the source and drain regions was conceptually sound, in practice it *did not work* because aluminum could not survive the follow-on high temperatures steps necessary to complete the process, *after* the aluminum had been deposited. In particular, it was impossible to repair the radiation damage done to the silicon crystal structure by the ion implantation. Thus, Bower's idea was good in principle, but a more refractory gate material than aluminum was needed. Bower's process was described in [1] but it was never used to produce commercial integrated circuits, and his process was unknown before the publication date of his patent. I independently developed in early 1968 a process architecture similar to his, but using polycrystalline silicon instead.

In 1967 John C. Sarace and collaborators at Bell Labs fabricated discrete transistors with gate electrodes made of vacuum-evaporated amorphous silicon, successfully

building working self-aligned gate MOS transistors [2]. Their experiment started with a wafer in which they grew a thin oxide, followed by vacuum deposition of amorphous silicon. They then masked the silicon to define the gates, which were shaped like annular regions. They then etched away the thin gate oxide, except where it was protected by the silicon gates. Finally they doped the wafer with boron to create the source and drain junctions. After a thin layer of oxide was grown over the entire structure, the following sequence of steps was performed: contact mask, aluminum evaporation, and metal mask; thus completing the process in the usual way.

The ring structure of the gate created the drain electrodes inside the ring, while the source electrodes of *all* the transistors were connected together, since it was the common diffusion outside all the rings. Therefore, the process they described was useless for the fabrication of integrated circuits; it was just a proof of principle, suitable only for the fabrication of *discrete transistors*, and was not pursued further by its investigators.

In late 1967, Tom Klein of Fairchild Semiconductor, experimented with MOS capacitors, called CV dots<sup>3</sup>, where the aluminum was replaced with heavily-doped P-type amorphous silicon. He observed that the work function difference between the doped amorphous silicon and the lightly doped single-crystal N-type silicon was 1.1 volt *lower* than the work function difference between aluminum and the same N-type silicon. This meant that the threshold voltage of MOS transistors built with silicon gate could be 1.1 volt lower than the threshold voltage of MOS transistors with aluminum gate fabricated from the same starting material. Therefore, starting with [111] orientation silicon, it was possible to simultaneously achieve both low-threshold-voltage MOS transistors and high field-oxide threshold voltage.

Tom Klein thus established that by using P-type doped silicon gate it would be *potentially* possible not only to create self-aligned gate transistors, but also to achieve a low threshold voltage process, using the same crystal orientation employed in the high threshold voltage MOS process. However, Klein could not figure out how to *architect* the process to make the isolated transistors necessary for the fabrication of self-aligned-gate integrated circuits. At this point I enter the picture, and I will continue the story with a first-person narrative, after a brief description of my background.

#### 4.3 Before Silicon Valley

Born, raised and educated in Northern Italy, I graduated in 1960 in radio technology from the A. Rossi Technical Institute in Vicenza at the age of 18. During my senior year in school, I became interested in computers, reading everything I could find about them. My first job in 1960, was assistant engineer at the Olivetti Electronic R&D Laboratory near Milan, Italy, where Olivetti was developing their early electronic computers. Due to a series of fortunate circumstances, I ended up co-designing and building a small experimental electronic computer with 4k 12-bit words of magnetic core memory. I was 19 years old and I had four technicians working for me, helping me with the construction

$<sup>\</sup>binom{3}{3}$  CV-dots was a technique used in the 1960's to test the cleanliness of silicon dioxide. It consisted in evaporating small aluminum dots through a metal mask with small holes in contact with oxidized silicon. This method allowed to quickly measure the capacitance-voltage relationship of small capacitors, and to also measure the threshold voltage drift with temperature, without having to perform a photolithographic and etching process to define the capacitors.

of that computer. The computer used approximately 1000 logic gates made with germanium transistors (fabricated in Italy by SGS), requiring about 200 small PC boards, housed in several card cages that were mounted on a single equipment rack. This early experience turned out to be absolutely invaluable, setting the stage for much of my future career.

At the end of that successful project I decided to return to school and study physics at Padua University, because I wanted to deepen my understanding of solid state physics. Since I needed to complete my Olivetti project, I began university in January 1962, a few months after the academic year had already started, forcing me to study incessantly to catch up. I studied with much pleasure and I graduated in October 1965, receiving a *laurea* degree in physics (the only university degree in Italy in those days), summa cum laude, with an experimental thesis on flying spot scanners. I was given a job at the University as soon as I graduated, and I taught Electronics Laboratory to 3<sup>rd</sup>-year physics students during the 1965-1966 academic year.

In the summer of 1966, I decided to leave the university and join CERES, a startup company in the Milan area, to work for my old boss at Olivetti, who now was the head of this company. CERES was developing thin film circuits, and was also the Italian agent of GMe, General Micro-electronics, Inc., the world's first MOS company. GMe had started in Silicon Valley a couple of years earlier with founders coming from Fairchild, and its first commercial MOS product was a 20-bit shift register. Unbeknownst to me, GMe was struggling to make reliable MOS ICs.

My first assignment at CERES was to take a one-week course at GMe in Sunnyvale, California, on MOS technology. This was necessary to be able to properly explain the GMe product line to potential customers in Italy. My trip to Silicon Valley was my first intercontinental journey, and I found the San Francisco Bay Area immensely energizing. After my return to Italy, CERES received an order for a few 100-bit MOS shift registers – the most recent product of GMe – from the University of Rome. Unfortunately, GMe could never deliver, and before long it was sold to RCA, thus ending the relationship with CERES.

That one-week course on MOS technology, however, landed me a job at SGS-Fairchild in Agrate Brianza, Italy in 1967. SGS-Fairchild was at that time the only Italian semiconductor company, 30% owned by Fairchild Semiconductor, and a licensee of Fairchild's bipolar technology. I worked in the newly-formed R&D department of SGS, and given my brief exposure to MOS, I was assigned the job of developing their first MOS process technology. When the process was done, I also designed the first two commercial MOS IC products for SGS, which I successfully completed in early 1968 [3]. A few months later I was promoted to the position of MOS group leader.

In September, 1967 I married Elvia Sardei and settled in an apartment in Agrate Brianza. Elvia grew up in Vicenza, like me, and attended the same university in Padua where we had met several years before. Toward the end of 1967, SGS asked me if I was interested in going to the US for 6 months, as part of an engineer exchange program between SGS and Fairchild. I jumped at the opportunity to return to Silicon Valley, and Elvia was excited as well. We arrived in the San Francisco Bay Area in February, 1968, rented a small apartment in nearby Mountain View, and I worked in the R&D Laboratory of Fairchild Semiconductor in Palo Alto. It was the start of a great adventure!

I was supposed to stay for six months and then return to Italy, but while I was in the US, Fairchild sold its interest in SGS-Fairchild, and they asked me to stay. That's how Elvia and I decided to make Silicon Valley our new home.

#### 4.4 Developing the SGT and the first commercial IC with SGT

In February 1968, I joined the MOS process development group of the Fairchild Semiconductor R&D Laboratory in Palo Alto, CA, then directed by Les Vadasz. I was a guest engineer, and my US boss was Les Vadasz, who immediately gave me the choice between two projects: (1) designing a special shift register chip or (2) developing a self-aligned-gate MOS technology using silicon gates. I chose the latter since I was well aware of the deleterious effects of the parasitic drain to gate capacitance in MOS transistors. I was not aware, however, of the previous work done at Bell Labs and at Hughes Aircraft. I learned about the Bell Labs work only after I had successfully completed the project, and about the Hughes Aircraft work many years later. But I was told, of course, about the experiments of Tom Klein with CV dots, and about the concept of self-alignment, which I had already heard before. What no one at Fairchild had yet devised was the necessary process architecture to make integrated circuits with silicon gate.

When I started at Fairchild, it wasn't even known how to precision-etch thin films of silicon. Therefore, my first tasks were: (1) to invent the process architecture for self-aligned silicon gates, (2) to develop a method to precision-etch the amorphous silicon, and (3) to design the detailed processing steps to fabricate MOS ICs with silicon gates. To be able to characterize the process, I also had to design a suitable test pattern that would allow me to measure all critical parameters. If all worked well, I would then have to design an appropriate commercial integrated circuit to convincingly prove the superior performance and reliability of the new technology.

For many days I struggled trying to figure out how to architect the process. I asked all the local experts how they would do it, but I got nowhere. After a week or so it donned on me that if I started with etching a *tub* into the initial oxide where the *entire* MOS device was supposed to be, I could then solve the problem. Only then did I realize how much I had been conditioned by the old way of making MOS transistors where the first step was to define *only* the source and drain of the device. The "tub" was the missing insight about how to make self-aligned gate MOS ICs.

The next problem was how to connect the silicon gates to the source and drain junctions in the most efficient manner. Obviously one could use an aluminum strip to connect the silicon gate to the appropriate junction, but that would require a lot of area. Desiring a better solution, I came up with the idea of making a *buried contact*, which consisted in directly connecting the amorphous silicon to a junction without using metal. This method required an additional masking step, but it would considerably increase the circuit density because metal could now run over the buried contact. Having already some experience with chip layout, I appreciated this possibility since the density of conventional MOS circuits was severely limited by the metal interconnections. The addition of the buried contacts to the silicon gates that were also "buried" under oxide, would afford the same interconnection density achievable with two layers of metal, at the cost of only one additional masking step.

The alternative way of making the smallest possible silicon-to-junction contact was to

overlap the amorphous silicon onto a portion of the tub, then opening a contact large enough to overlap both the silicon and the junction area. The contact area would be covered with a dash of metal, completing the connection. This type of contact was called "butting contact." It was relatively small, but it penalized the interconnection density, particularly for random logic circuits where the interconnections dominated the overall circuit density. For example, using the SGT with only butting contacts, the chip area of the first microprocessor could have been reduced by about 30% over the area required with metal-gate MOS. Using SGT with *buried* contact, the chip area could be further reduced by about 40% over the SGT with butting contact; this amounted to half the size of the metal-gate version!

These were impressive numbers because the chip cost is proportional to the chip area divided by the yield (the wafer yield is the number of good chips divided by the total number of chips in a wafer). Now, the yield decreases with increasing chip size, slowly at first for small chips, but rapidly as the chip size approaches a limit, called maximum chip size, beyond which the yield is too small for the chip to be manufacturable<sup>4</sup>. Given this yield behavior with growing chip size, saving 40% of the area when a chip is approaching the maximum chip size, reduces the cost far more than 40%.

In summary, the process architecture I devised was to first open the areas in the initial oxide where the source, drain and gate of each transistor were to be located (tub mask). This step was then followed by the growth of the gate oxide, and followed by the vacuum-deposition, masking and etching of the silicon layer, thus defining the gates and the silicon interconnection layer. Next, the thin oxide was etched inside the tubs where it wasn't protected by the poly-silicon, thus defining the source and drain regions of the transistors. Notice here that the process is properly called *self-aligned* because a misalignment between the tub mask and the gate mask would only slightly change the geometry of the source and drain regions, but would not change the gate overlap capacitances of the transistors.

After the removal of the thin oxide, the source, drain and amorphous silicon would be doped with boron, and here the silicon gate would act as a mask against the doping occurring in the gate region. After doping, a thin layer of the best possible oxide would be thermally grown to protect the exposed source, drain and gate areas, followed by the deposition of a thicker layer of good quality vapox (which required a higher temperature than could be tolerated by aluminum). Contact mask, contact etching, aluminum deposition, metal mask, and passivation would then complete the process [4], [5], [6].

I also proposed a variant of the above process to make buried contacts, as follows: After the gate oxide was grown in the tubs, the gate oxide was removed in the areas where the buried contacts between silicon and junctions were to occur. Then the processing steps following the buried contact mask continued as previously described. The idea here was that when the boron doping would be performed, boron atoms would completely diffuse *through* the thin layer of deposited silicon in contact with the singlecrystal silicon of the wafer, forming a junction in the single-crystal silicon itself, thus

<sup>(&</sup>lt;sup>4</sup>) The maximum chip size depends on the defect density achievable with any particular process, at any particular time. One of the key improvements responsible for Moore's law has been a relentless reduction of the defect density, between 1968 and today, by more than a factor of  $10^6$ .

creating an *isolated* contact that would later be protected by oxide. Therefore, aluminum could go right above the buried contact, allowing a greater circuit density to be achieved.

When ten days after my arrival I described to Vadasz how I proposed to make silicon gate ICs, he approved my proposed process architecture, but said that the buried contact would never work and when I respectfully disagreed, he didn't even want me to try it out. Vadasz had a forceful management style and I decided not to argue with him, but when a few weeks later I designed the test pattern necessary to properly characterize the new technology, I decided to place a couple of structures in it that would allow me to verify if the buried contact would actually work, and also to characterize its properties. I disobeyed because it cost nothing to do so, and I strongly believed in my idea.

The next step was to develop a suitable silicon etching solution. Again, nobody knew how to do that. I finally found a chemical engineer, and I asked him what he would do. He suggested I read a paper that described how to chemically attack silicon with a mixture of nitric acid and hydrofluoric acid. Therefore I decided to experiment with a *dilution* in deionized water of different proportions of the two acids. By trial and error, I found the best ratios to give me an optimal differential etching rate between silicon and silicon dioxide, while achieving a negligible undercut under the photoresist. It took about ten days and a new pair of shoes to reach the goal; the shoes being the victims of a drop of the mixture falling on my right foot. Fortunately the etching of my right shoe ended just before reaching my skin.

In parallel with that task I designed a test pattern, called XTPG, containing all kinds of structures suitable to determining the various parameters of the MOS transistors; the resistivity of various thin films, the contact resistance of various contact geometries, and so on. The last step was to define and calculate all the detailed processing conditions to complete the "run sheet." The run sheet was the list of materials, operations, equipment, and conditions that accompanied a batch of wafers, called a *run*, going through the wafer fab. It described in a step-by-step sequence all the operations to be performed on a batch of wafers, from the very beginning to the end of the process.

By April, 1968 I was able to fabricate the first working MOS transistors with silicon gate, suitable for making integrated circuits, going through the entire silicon gate process. Since the characteristics of these first devices were quite promising, it was now time to design the first integrated circuit using the new self-aligned process, and compare it with a similar production metal-gate device. Vadasz asked the production people what was their most difficult IC to produce. They said it was the Fairchild 3705, an 8-bit analog multiplexer with decoding logic – a chip with stringent processing requirements.

The 3705 consisted of 8 very large transistors that had to behave as close as possible to ideal switches. This meant that when a transistor was turned on, it had to have a very low on-resistance; and when it was turned off, it had to have a very low leakage current. The chip also contained a decoder, so that each "switch" could be selected by simply using a 3-bit address. In addition, the switching speed had to be fairly high; which was another difficult requirement to meet. The worst parameter to control, however, was the low leakage current, made worse by the large size of the transistors.

The idea was to design a chip that was functionally identical to the 3705, but used the SGT instead. In this manner, the characteristics of the SGT chip could be easily compared one-for-one to the characteristics of the metal-gate version, facilitating the evaluation of the new technology. The new chip was called 3708 and it was hoped that, if

everything worked well, the 3708 could replace the 3705, given the production difficulties of the latter. The 3708 also provided the platform to further evaluate the SGT and to improve the process, if necessary, during the following months.

It took me a couple of weeks to complete the 3708 design and the composite layout of the chip, with the help of a layout draftsman. Then the laborious process of creating the masks needed to process the wafers started. That entire process took several weeks, and finally, by early July, I had the first wafers of the 3708. When I tested it, it worked immediately, and I could also see that its performance was much superior to the 3705. That made me very happy.

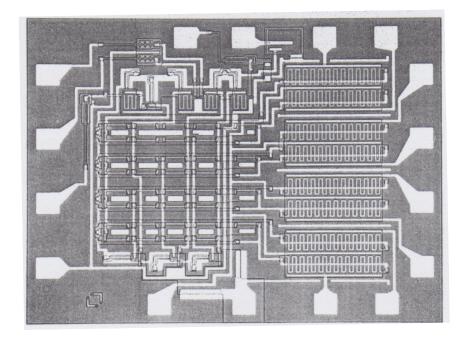

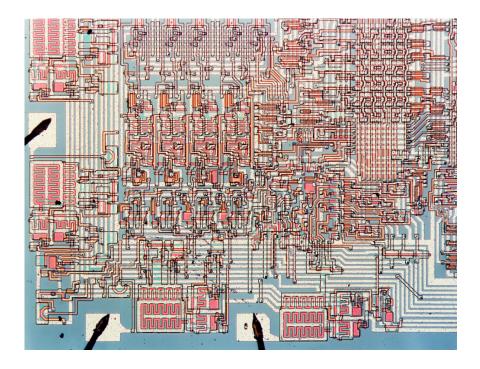

With a fully functioning 3708 (See Fig. 1), I could now start the characterization of the 3708 and also complete the process characterization. This last task was accomplished by having a few XTPG test patterns interspersed in the same masks used for the 3708. Therefore, both process and chip characteristics could be measured. Additionally, the characterization required that special runs be performed by purposefully manipulating certain critical parameters to generate a set of worst-case conditions able to simulate the expected variations in the manufacturing process over the lifetime of the product.

It was during this characterization process that I found to my dismay that the amorphous silicon tended to break at the large oxide steps created by the tub mask. This discovery should not have been surprising since the amorphous silicon was vacuum-evaporated using the same equipment and methods used for the aluminum evaporation, where such problems were already well known. Therefore, the same self-shadowing responsible for aluminum breakage was also at work for the silicon film, except that the situation was worse for silicon.

Fortunately, there was another possibility for creating silicon films at Fairchild. This method used the chemical decomposition of silane (SiH<sub>4</sub>), at low pressure and at temperatures ranging from  $650^{\circ}$  to  $750^{\circ}$ C. This method produced *polycrystalline* silicon rather than amorphous silicon, with grain sizes up to 10nm, dependent on the growth conditions. Because the new deposition method created near-chaotic atomic trajectories, rather than the directional *rays* of aluminum particles responsible for the self-shadowing in the vacuum deposition process, the step coverage was excellent, and the problem was elegantly solved.

Sometime later, I found out that the bipolar group had developed a process to soak up, so to speak, and eliminate much of the highly mobile impurities present in the wafer prior to the contact mask and metal deposition. This process consisted in the deposition of a layer of vapox, followed by heavy doping with phosphorous of both the topside oxide and the bottom side silicon, followed by a thermal treatment at temperatures between 800° and 900°C. Under those conditions, the phosphorous acted like a *sponge*, locally segregating impurities which would then diffuse from the wafers toward the phosphorous layers and be segregated there. The impurities could then be eliminated by etching the highly doped layer of silicon in the backside of the wafer and the doped layer on the topside oxide. This process was called phosphorous gettering and resulted in much lower junction leakage currents and higher long-term reliability.

Phosphorous gettering, however, could not be used with the metal-gate MOS process because the aluminum would short the junctions at temperatures above 600°C. Therefore, the junction leakage current of MOS devices was dominated by the effect of the impurities already present in the starting material, plus the impurities accumulated during

the manufacturing process. Since the silicon gate could easily withstand the phosphorous gettering temperature, this process could be easily added to the existing process flow, *after* the MOS transistors had been fabricated, and after they had been sealed in the best possible material. This was silicon dioxide (quartz), thermally grown at 1200°C. The results were outstanding: the junction leakage current was reduced by more than a factor of 100, and the threshold voltage drift that still occasionally plagued MOS devices made with aluminum gates, was eliminated.

Fig. 1. – The Fairchild 3708, the world's first commercial self-aligned gate MOS IC with SGT, first sold toward the end of 1968.

At last, the MOS ICs long-term reliability achieved the same level enjoyed by bipolar ICs, removing another major obstacle to the broad market adoption of MOS technology. Reducing the leakage current to this low level proved of fundamental importance in the development and acceptance of dynamic random access memories (DRAM), in which the information is stored as electrical charges in the gate capacitances of MOS transistors. In this case, since the gate is inevitably connected to a junction, the leakage current of that junction will discharge the electrical charge that represents the informational bit.

After the characterization was completed, the silicon gate technology had achieved impressive results: Compared with the 3705, the 3708 was 5 times faster, it had about 100 times less leakage current, and the on resistance of the analog switches was 3 times lower [4], [5], [6]. The Fairchild marketing department decided to sell the 3708 chips that were produced in the R&D Lab, after their reliability was proven by the production QA engineers. The first sale occurred toward the end of 1968, and continued with R&D wafers until the process was transferred to the MOS division in Mountain View. In the interim, I did provide the wafers to the production department.

Remarkably, the cost of setting up a fab in the 1960's was a very small fraction of what it cost today. Therefore, in the R&D division there were several independent fabs. One of them was the fab of the digital integrated electronics department, the department headed by Bob Seeds, to which our MOS group belonged.

### 4.5 New Developments

June, 1968 was a memorable month. First, the SGT development was progressing very well. Then, in the middle of June, I was told that my project had been selected for presentation at the upcoming IEDM Conference to be held in Washington D.C. the following October, and I gave a dry-run presentation to Gordon Moore, the head of the R&D Laboratory. This would have been my first public presentation to an international conference, and I was quite happy that my work had been chosen. But I was also surprised that management wanted to disclose this project so soon, before it was completed. I was 26 year old, still learning to be proficient in English and trying to figure out the American ways; I reckoned that this was the way it's done in America. That same month Fairchild also decided to sell their interest in SGS-Fairchild, and I was offered a job at the R&D Lab to continue my work, which I gladly accepted since by that time I had no desire to return to Italy. Elvia and I both felt that life in Silicon Valley was far more exciting than in Agrate Brianza!

My official starting date as an employee of Fairchild, was July 1<sup>st</sup>. And that day the laboratory was abuzz with the rumor that Robert Noyce, the head of Fairchild Semiconductor, and Gordon Moore who reported to him, were leaving Fairchild to start a new company. Soon after Noyce and Moore left, many other Fairchild employees quit to join the new company. Andy Grove, who was Moore's assistant, left one week after his boss, and Vadasz, a friend of Grove, left within two weeks after Grove's departure. The name of the new company was Intel. I suspected immediately that Intel would use the SGT because of the strong interest shown by Vadasz, Grove and Moore in my project. That suspicion was reinforced when, about one month later, Intel also hired the technician who was doing the amorphous silicon evaporation for my experiments.

Tom Klein took over the position vacated by Vadasz, and became my new boss. Klein, Vadasz, and Grove were Hungarian born, and they all had fled Hungary in the 1956 uprising, though they didn't know each other in Hungary. Klein made no secret to me that he expected to be asked to join Intel sometime soon. But this never happened.

## 4.6 Designing Circuits with the SGT

Toward the end of 1968, Fairchild's management made the decision to transfer the SGT process to the production fab that belonged to the MOS operating division. My job was essentially done, though I had to assist the production team to explain the fine points if necessary, and in case of problems. I was also writing a voluminous report on the SGT that was part of the internal Technical Report Series so that other departments within Fairchild R&D could use the process. I was expecting that the production engineers and the professional chip designers of the MOS division would be excited to have such a superior technology. But that was not the case. Despite the success of the 3708, the division was resisting the adoption of the SGT. My contact in the division was telling me that the design engineers were complaining that the circuit layout with SGT used more area than metal gate did.

This was my first encounter with what is called the *NIH syndrome*. NIH stands for notinvented-here, meaning that often engineers refuse to consider worthwhile anything that isn't invented in their own group – even if it is invented in the same company. It is a typical malaise of large companies, a prevalent cultural problem that Fairchild had, even if its size was not yet very large. In fact, at Fairchild there was real animosity between the R&D people and the operating divisions, with finger-pointing in both directions. The division guys complained that they were paying the bills while the haughty R&D guys thought they were so much smarter than them, and only cared about their own theories and projects. For their part, the R&D guys thought that the division guys had no vision and only cared about getting their immediate problem solved.

I began to understand why people leave companies to start new businesses, and why startup companies are necessary to bring new ideas into the world. I realized, if only faintly at that time, that if a company doesn't have a strong culture of innovation, it will resist new ideas because new ideas mean *change*, and change always brings new risks, requires extra effort, and opposes *routine*, which is what many people want.

When I got the feedback that the layout with SGT took more area than metal gate, I asked to be shown the trial layouts done by the division chip designers. I was flabbergasted when I saw what the engineers had produced: they had automatically translated into silicon-gate the old aluminum-gate circuit topologies, without the necessary rethinking, given the substantial differences between the two technologies. In other words, their layouts were done by following the same *implicit rules and style* they used with metal gate technology, when SGT required instead a different style. No wonder they found no advantage with SGT!

Those poor results demonstrated to me that I should not have taken for granted that engineers would understand how to take advantage of the new technology without being given examples of how to do it. I was so close to my creation that for me it was obvious what needed to be done; but not to them. Therefore, I showed them how I would layout their same circuits, proving my contention that SGT was much denser than metal gate, particularly if buried contacts were used.

I didn't hear much else for a while, until I was told that the SGT was not good because it didn't allow the fabrication of isolated capacitors. When I asked why they needed those capacitors, I was told that their main application was to make bootstrap load devices. True, SGT didn't allow making isolated capacitors for the simple reason that the polysilicon over thin oxide would block the formation of a junction underneath. That was in fact the entire point of the self-aligned gate. Their objection was valid, and I fully understood the implications, even though I personally believed that the advantages of the SGT were big enough to warrant the cost of an additional masking step. But that was not the conclusion of the managers. Finally, I got to the bottom of why the design engineers resisted using the SGT.

The importance of the so-called *bootstrap load* was to allow a logic gate to achieve an output voltage swing equal to the supply voltage, VDD, rather than (VDD - Vt), which is the maximum output voltage produced by a conventional MOS transistor load with threshold voltage Vt. Bootstrap loads empowered a very efficient design technique widely used in those days, called two-phase-clock dynamic logic. This technique was also called quasi-static design because it allowed mixing static with dynamic logic circuits.

Now, to make quasi static circuits it was necessary to use pass transistors, i.e.

transistors connected to the gate of other transistors. This allowed the temporary storage of information in the gate capacitance of the transistor driven by the pass transistor in the form of an electrical charge. This capability dramatically reduced the number of transistors needed for random logic circuits, compared to a fully static design. It was also a key reason why MOS technology required far fewer transistors than bipolar technology to realize logic functions. For example, with a pass transistor, a dynamic D flip-flop could be made with three transistors, while a *static* D flip-flop required 10 transistors. A D flip-flop made with bipolar technology required more than 15 transistors.

When (VDD - Vt) is applied to the gate of a pass transistor, however, the maximum voltage on the gate connected to the pass transistor is one *additional* threshold voltage drop below (VDD - Vt). Unfortunately, this new signal is generally not sufficient, in worst-case conditions, to turn on that transistor. And this was why the bootstrap load was indispensable to the realization of complex dynamic logic ICs: it allowed a logic gate to drive the gate of a pass transistor with a voltage equal to VDD when that gate had a bootstrap load rather than a conventional load.<sup>5</sup> Without bootstrap loads, it was impossible to design the complex logic circuits where the output of a logic gate could drive pass transistors, although two-phase-clock shift registers or other simple logic gates could be made, as long as the clock voltage swing was equal to VDD.

The other indispensable circuit where bootstrap loads were required was the push-pull buffer. Push-pull buffers were necessary whenever a logic gate had to drive a large capacitive load without dissipating an inordinate amount of power (the data-bus drivers had to drive several hundred pF of capacitive load). And this was absolutely necessary in any complex random logic circuit. The bottom line was that to make complex MOS random logic circuits in 1970 there were only three practical approaches: (1) using 2-phase dynamic logic circuits with bootstrap loads for push-pull and logic; (2) using 4-phase dynamic logic circuits with bootstrap loads for push-pull; and (3) using fully static circuits, which required many more transistors and much more power dissipation than dynamic circuits, for any given speed.

Without bootstrap loads, the world's first microprocessor, the Intel 4004, would not have been feasible in 1970 because it would have required a fully static design, resulting in a chip too large to be made with acceptable yield, and too slow to be useful, unless the allowed power dissipation was much greater than available commercial packages could handle. For example, military applications could use proprietary packages with high

<sup>(&</sup>lt;sup>5</sup>) To fully understand the situation, one needs to know the so-called *body-effect*, where the body is the common substrate of the chip whose electrical potential is shared by all the transistors in the IC. The threshold voltage of a transistor whose source is at a different potential with respect to the body, or substrate, is augmented by an amount proportional to the square root of the source-to-body voltage, *VSB*. In other words, *Vt1*, is function of *VSB*, which is also the output voltage of the logic gate, *VO1*. This is the body-effect. Therefore,  $Vt1 = VT1 + k\sqrt{VSB} = VT1 + k\sqrt{VO1}$ , where *VT1* is the threshold voltage of the load transistor with VSB = 0; and k is the proportionality constant of the body effect. When a logic gate drives the silicon gate of a pass transistor, the maximum voltage at the output (the source) of the pass transistor is  $VO2 = VDD - (VT1 + k\sqrt{VO1}) - (VT2 + k\sqrt{VO2})$ , where VT2 is the threshold voltage of the transistor with its *VSB* = 0. Therefore, VO2, under worst case conditions, can be insufficient to drive the transistor connected with the pass transistor. However, if the output of the logic gate is VDD, then  $VO2 = VDD - (VT2 + k\sqrt{VO2})$ , which is exactly like the output voltage of any other logic gate.

power dissipation and large chip size, which meant very high cost due to low yield; prohibitive conditions for non-military applications.

When I heard about the bootstrap load, I couldn't let that difficulty thwart the unconditional use of the SGT. Therefore I kept on thinking about how I could solve this thorny problem. It took me about nine months to figure out how to design bootstrap loads without adding another mask. The solution, when I founded it, was actually very simple. This of course is very typical of most engineering problems.

Then one day I noticed that the metal electrode of the capacitor in a metal-gate bootstrap load was always biased in such a way that it would create an *inversion layer* in the silicon below *even if there was no diffusion* under the gate oxide. In other words, the operating conditions of the bootstrap load were such that there was a "virtual" diffusion below the metal electrode at all times. Therefore, if I replaced the metal with a silicon electrode, I would have as good a capacitor as if there was a real diffusion underneath. All I needed to do was to create a large area in the tub mask corresponding to the drain of the bootstrap load transistor, and create a poly-silicon region, *inside* this area so that the inversion layer beneath the poly-silicon would be surrounded by a junction area connected with the drain of the load transistor.

This was another key insight, just like when I got the idea of the tub mask – the missing idea to making self-aligned *isolated* transistors. And it felt exactly the same way: a rush of exultation; the "Aha!" of a deeper comprehension. Something like, "I got it! I cracked the nut!" Finally there was nothing more standing between me and the success of the SGT! I proceeded to design a test chip with different geometries of bootstrap loads to find out how well the idea worked, and also to characterize the circuit. I verified that the bootstrap load worked perfectly, shortly before deciding to leave Fairchild. Now my job had been done to the very end.

After Vadasz left Fairchild to join Intel, I also fabricated and tested the buried contact, the invention that Vadasz did not approve of. I verified that the idea worked perfectly, and I made a number of test layouts to prove to myself that with buried contacts I could make significantly more compact layouts, particularly for random logic circuits. With the addition of the buried contact and the bootstrap load, the SGT was now in all respects better than the incumbent metal gate technology, allowing a designer to integrate in the same chip size about twice the number of random logic transistors and achieve about 5 times the speed of the incumbent technology – when using two-phase clock designs with the same power dissipation of an equivalent metal-gate design.